# THE SWITCH

# LNDoubler 5/8

#### FEATURES

- 5- and 8-inch\* disk drives

- · Single- & double-density

- · Any size and density in any mix

- Read Model I, II\* and III disks

- 5- or 8-inch\* system disk

- · Single & double sided disk drives

- DOS+ 3.3.9 included, with Disk BASIC.

- · 6 month warranty

- · Up to 3.75 megabytes online

- · Easy installation plug-in & run

- Analog phase lock loop data separation

- · Precision write precompensation

- · Regulated power supply

- Guaranteed operation at 4MHz

- · All contacts gold plated

- · Solder masked & silk screened

- Runs under DOS+ 3.3.9, TRSDOS 2.3, NEWDOS 2.1, NEWDOS/80 1.0, LDOS, NEWDOS/80 2.0, and ULTRADOS

- Reads 40- and 35-track disks on 80-track drives

- FD1791 controller + your FD1771

- Fits Model I expansion interfaces

- Fits LNW expansion interfaces

- Track configurations to 80-tracks

- 5 inch disk storage increased to: 161,280 bytes – 35-track SS/DD 322,560 bytes – 35-track DS/DD 184,320 bytes – 40-track SS/DD 368,640 bytes – 40-track DS/DD

- 368,640 bytes 80-track SS/DD 787,280 bytes - 80-track DS/DD

591,360 bytes - 77-track SS/DD 1,182,720 bytes - 77-track DS/DD

SS: single-sided DS: double-sided SD: single-density DD: double-density COMPLETE - The LNDoubler 5/8,

into the most versatile computer you can own. The LNDoubler's switch allows you to boot from 5- or 8-inch system disks, and it's accessible from outside the interface. The LNDoubler

switches your Model I or LNW-80

outside the interface. The LNDoubler 5/8 comes with a double-density disk operating system (DOS+ 3.3.9),

complete with BASIC and utility programs... ready to run your software NOW!

VERSATILE – Whether you want single-sided, double-sided, single- or double-density, 5- or 8-inch operation, complete versatility is here today! Any combination of 5- and 8-inch disk storage is possible with the LNDoubler 5/8. Each of your present

40-track, single-sided 5-inch drives will store up to 184,320 bytes (formatted storage) – that's an 80% increase in storage capacity for only half the cost of just one disk drive.

With three 8-inch double-density, double-sided drives your Model I will have 3.75 Megabytes of online storage - that's more storage than a Model II or Model III!

ADVANCED - The LNDoubler 5/8 is the most technically advanced, tested and reliable double-density board you can buy. The LNDoubler

5/8 has more features, more options and more software support than any other product of its kind.

EASY TO INSTALL – The LNDoubler 5/8 is easy to install. There are no traces to cut, no wiring to do, just a screwdriver and a few minutes of your time is all that is required. The instructions are fully

illustrated for all interfaces. In minutes you will be 'up-and-running', and enjoying your computer as never

COMPARE - Compare features, compare quality, compare value, and make the SWITCH today!

Immediate delivery from stock - at your dealer NOW for only

°199.95

without DOS

\$219.95

with DOS

DEALERS - You too can make The Switch.

2620 WALNUT Tustin, CA. 92680

(714) 641-8850 (714) 544-5744

#### LNDOUBLER 5/8

The ultimate in double density adapter units

USER MANUAL VERSION 1.0 08/29/81

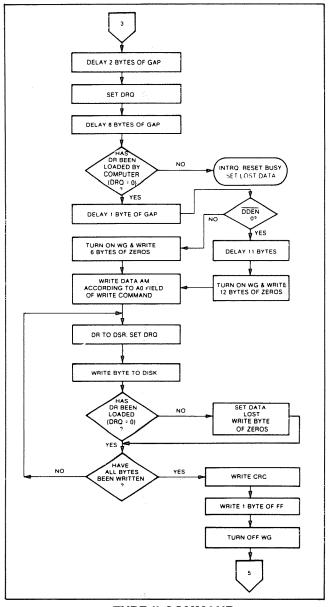

|  | *3   |

|--|------|

|  | ~    |

|  |      |

|  |      |

|  |      |

|  |      |

|  |      |

|  |      |

|  |      |

|  |      |

|  |      |

|  |      |

|  |      |

|  |      |

|  |      |

|  |      |

|  |      |

|  |      |

|  |      |

|  |      |

|  | 8    |

|  | •    |

|  |      |

|  |      |

|  |      |

|  |      |

|  |      |

|  |      |

|  |      |

|  |      |

|  |      |

|  |      |

|  |      |

|  |      |

|  |      |

|  |      |

|  |      |

|  |      |

|  |      |

|  |      |

|  |      |

|  |      |

|  |      |

|  |      |

|  | er . |

|  |      |

|  |      |

|  | ¥    |

|  |      |

|  |      |

|  |      |

|  |      |

|  |      |

#### CONTENTS

| INTRODUCTION1                          |

|----------------------------------------|

| MEDIA AND DISK DRIVE REQUIREMENTS2     |

| REQUIRED ACCESORIES                    |

| TESTING YOUR INTERFACE4                |

| INSTALLATION INTRUCTIONS5              |

| RADIO SHACK EXPANSION INTERFACE6       |

| OLDER VERSION OF EXPANSION INTERFACE7  |

| NEWER VERSION OF EXPANSION INTERFACE11 |

| LNW RESEARCH SYSTEM EXPANSION15        |

| ASSEMBLED AND TESTED15                 |

| KIT FORM18                             |

|                                        |

| POWERING UP FOR THE FIRST TIME19       |

| CONNECTING EIGHT INCH DISK DRIVES20    |

| TROUBLESHOOTING22                      |

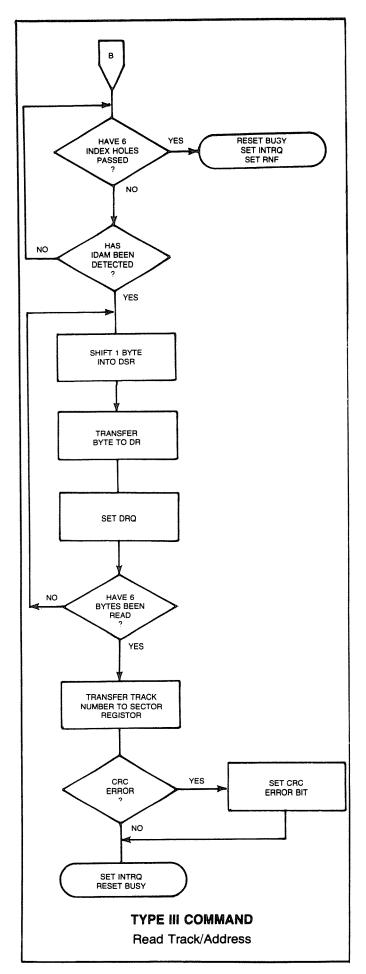

| THEORY OF OPERATIONS                   |

| FD179X-02 FLOPPY CONTROLLER DATA28     |

| WD1691 FLOPPY SUPPORT LOGIC DATA44     |

| FD179X APPLICATION NOTES47             |

| ALIGNMENT53                            |

| ACCESSORY ORDERING INFORMATION54       |

| LIMITED WARRANTY55                     |

| ACKNOWLEDGEMENTS56                     |

| APPENDIX 1.0 USING NEWDOS80 2.057      |

|  |  | ıl |

|--|--|----|

|  |  |    |

|  |  |    |

|  |  | ч  |

|  |  |    |

|  |  |    |

|  |  |    |

|  |  |    |

|  |  |    |

|  |  |    |

|  |  |    |

|  |  |    |

|  |  |    |

|  |  |    |

|  |  |    |

|  |  |    |

|  |  |    |

|  |  |    |

|  |  |    |

|  |  |    |

|  |  |    |

|  |  | 창  |

|  |  |    |

|  |  | •  |

|  |  |    |

|  |  |    |

|  |  |    |

|  |  |    |

|  |  |    |

|  |  |    |

|  |  |    |

|  |  |    |

|  |  |    |

|  |  |    |

|  |  |    |

|  |  |    |

|  |  |    |

|  |  |    |

|  |  |    |

|  |  |    |

|  |  |    |

|  |  |    |

|  |  | ÷  |

|  |  |    |

|  |  | ٧  |

|  |  |    |

|  |  |    |

|  |  |    |

|  |  |    |

The LNDOUBLER 5/8 switches your TRS80\* MODEL I or LNW80 computer into the most versatile computer you can own. Whether you want single sided, double sided, single or double density, 5 or 8 inch disk operation, any combination of disk storage is possible with the LNDOUBLER 5/8. Each of your present 40 track single sided disk drives will store up to 184,320 bytes (formatted)-thats an 80% increase! The LNDOUBLER 5/8 even allows you to BOOT from an 8" system disk with a flip of a switch. The LNDOUBLER 5/8 is compatible with all software available for 5" single and double density,8" single and double density written for the TRS80.

The LNDOUBLER 5/8 is easy to install. There are no traces to cut, no soldering or wiring. Just unplug the floppy controller IC (FD1771) from your interface, install the FD1771 into the LNDOUBLER 5/8, and just plug the LNDOUBLER 5/8 into the interface. In just a few minutes you'll be enjoying your computer as never before.

The LNDOUBLER 5/8 is the most technically advanced, tested and reliable double density board you can own. The LNDOUBLER 5/8 has more features, more capabilities, and more software support than any product of it's kind.

#### **FEATURES**

- \* RELIABLE OPERATION GUARANTEED WITH ALL 5.25" and 8" DISK DRIVES

- \* SINGLE AND DOUBLE DENSITY OPERATION

- \* 5.25" AND 8" IN ANY MIX

\* READ MODEL I, II, III DISKS

- \* 5.25" AND 8" SYSTEM DISKS

- \* ANALOG PHASE LOCK LOOP DATA SEPARATION

- \* PRECISION WRITE PRECOMPENSATION

- \* REGULATED SUPPLY FOR VCO AND ALIGNMENT CIRCUITS

- \* GUARANTEED OPERATION WITH ALL TRS8Ø EXPANSION INTERFACE UNITS

- \* ALL GOLD CONTACTS

- \* GUARANTEED OPERATION AT 4.0 MHZ CPU SPEED

- \* EASY INSTALLATION

- \* COMPATIBLE WITH ALL SINGLE, DOUBLE AND 8" DRIVE SOFTWARE

- \* FIVE INCH DISK STORAGE INCREASED TO :

- 161,280 bytes- 35 track ss/dd

- 322,560 bytes- 35 track ds/dd

- 184,320 bytes- 40 track ss/dd

- 368,640 bytes- 40 track ds/dd

- 368,640 bytes- 80 track ss/dd

- 737,280 bytes- 80 track ds/dd

- \* EIGHT INCH DISK STORAGE INCREASED TO:

- 335,104 bytes- 77 track ss/sd

- 670,208 bytes -77 track ds/sd

- 591,360 bytes -77 track ss/dd

- 1,182,720 bytes -77 track ds/dd

- ss: single sided ds: dual sided

sd: single density dd: double density

#### MEDIA AND DRIVE REQUIREMENTS

Since the LNDOUBLER 5/8 will work with virtually any drive and any media, it may be tempting to use (for example) low cost single density single sided 35 track diskettes with 80 track, double density double sided drives. On the other hand, experimentation to find out which diskettes work the best, may lead to the conclusion that any diskettes will work. For this reason we at LNW RESEARCH make the following suggestions:

- 1.Use double density rated disk drives. Single density drives may work, but the proper operation in double density cannot be guaranteed for the life of the drive.

- 2.Use diskettes rated according to their use

- 3.Check diskettes for wear periodically

- 4.Clean and align your disk drive(s) according to the manufacturer's recommendations.

REQUIRED ACCESSORIES FOR 5" DOUBLE DENSITY,8" AND SPECIAL SOFTWARE APPLICATIONS

All existing TRS80 MOD I single density software will run unmodified in SINGLE DENSITY with the LNDOUBLER 5/8 installed. In order to use double density and 8" drive capabilities, special software is required. In order to connect an eight inch disk drive to your system, a special cable adapter circuit board and an eight inch disk drive cable (50 cond.) is required. Some eight inch disk drive software requires a special "wait cable" (stk# 1097). Some eight inch disk drives require that the "write current" line on the disk drive be driven when using these drives in double density above track 43.In order to do this another small cable is needed. This cable is called the "TG43 CABLE" (stk#1097). Shugart Disk drives DO NOT NEED THIS CABLE. Check the data sheets on your drive to determine if your drive needs this signal.

The hardware/software configuration information is summarized in the following table, and ordering information for the various accessories is included at the rear of the manual

| DOS           | 5.25" SD | 5.25" DD | 8" SD  | 8" DD  |

|---------------|----------|----------|--------|--------|

| Dosplus 3.2d  | X        | S        |        |        |

| Dosplus 3.38d | X        | S        | X(1)   | X(1,4) |

| Dbldos        | X        | S        |        |        |

| F.E.C. T8/OS  | S        |          | X(1,2) |        |

| LDOS 5.0      | S        | S        | •      |        |

| Omikron CP/M  | S        |          | S(1,2) |        |

| Newdos80 1.0  | S        | S(3)     | X(1,2) |        |

| Newdos8Ø 2.Ø  | S        | S        | S(1)   | X(1,4) |

| Vtos 4.0      | S        | S(3)     |        |        |

#### NOTES:

X= non system disk

S= system or non system disk

l= requires 8" cable adapter (stk#1096) and 8" drive cable (stk#1099)

2= requires "wait cable" (stk#1097)

3= requires Double Zap II from Software etc.

4= requires CPU speed to > 3.5 mhz or LNW80 computer SEE PAGE 21 for details concerning speed up kits

| C | ומ |   | T 7       | ١. | NO' | ጥፑ |

|---|----|---|-----------|----|-----|----|

| 5 | ۲. | Ľ | $\perp F$ | ۱L | NO. | ТĿ |

BEFORE ATTEMPTING TO INSTALL THE LNDOUBLER 5/8 INTO YOUR INTERFACE, MAKE SURE THAT YOUR INTERFACE IS FUNCTIONING PROPERLY. OPENING YOUR INTERFACE DURING THE LIMITED 90 (180 FOR LNW INTERFACE) DAY WARRANTY PERIOD MAY VOID YOUR WARRANTY. EXERCISE YOUR WARRANTY RIGHTS IF NECESSARY PRIOR TO INSTALLING THE LNDOUBLER

#### TEST YOUR INTERFACE

To test your interface and provide a "test diskette" for our initial power up of the LNDOUBLER 5/8, make a "backup" of a single density DOS SYSTEM disk.DO NOT attempt to BOOT the double density system disk (Dosplus) without the LNDOUBLER 5/8 installed. If you are not able to correctly backup a single density SYSTEM disk DO NOT attempt to install the LNDOUBLER 5/8. It cannot fix defective interface units! After backing up the single density SYSTEM disk attempt to BOOT this disk. If it boots correctly set it aside for the initial power up with the LNDOUBLER 5/8. Proceed to INSTALLATION INSTRUCTIONS.

#### INSTALLATION INSTRUCTIONS

TOOLS REQUIRED:

Small slotted screwdriver

Medium phillips screwdriver

Needle nose pliers or tweezers

Large clean work space

#### CAUTION

THE FD1771 FLOPPY CONTROLLER IC WHICH YOU WILL BE REQUIRED TO HANDLE DURING THE INSTALLATION OF THE LNDOUBLER 5/8 IS SENSITIVE TO STATIC ELECTRICITY AND CAN EASILY BE DAMAGED BY A STATIC DISCHARGE. BREAKING THE PINS OF THE FD1771 WILL ALSO CAUSE PERMANENT DAMAGE TO THE PART. WE MAKE THE FOLLOWING RECOMMENDATION CONCERNING THE HANDLING OF THE FD1771:

- 1. Work in an area that is NOT CARPETED

- 2. Do not wear clothes that will generate static

- 3. Have all tools close at hand before handling the FD1771

- 4. Use great care when removing and installing the FD1771 to not bend or break the delicate pins

Installation instructions are provided for the two different expansion interface units for the TRS80- the Tandy and the LNW interface.

#### TANDY INTERFACE

Disconnect the interface from the computer. Unplug the interface from the AC power, disconnect all cables from the interface (printer,RS232,and floppy disk,etc.). Turn the interface upside down such that the rubber feet face upward. You will notice six (6) phillips-head screws recessed into the plastic bottom of the interface case. Loosen each screw completely but don't remove them from the bottom panel.

Carefully lift the entire bottom panel away and set it beside the interface exercising care not to lose the mounting

screws. Note that the screws are of different lengths.

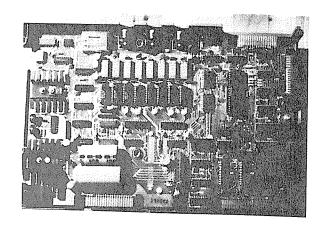

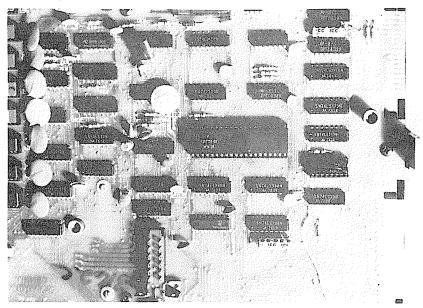

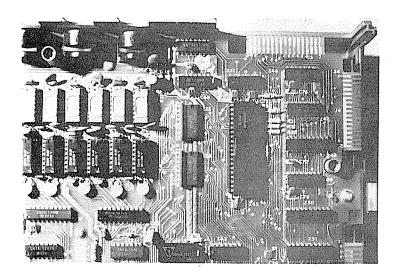

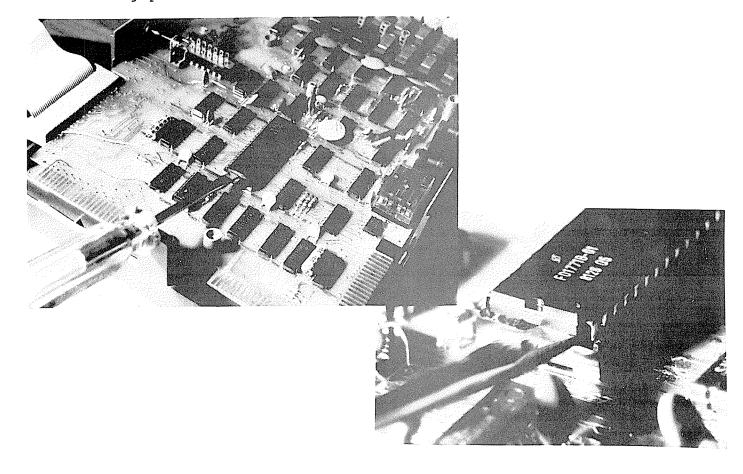

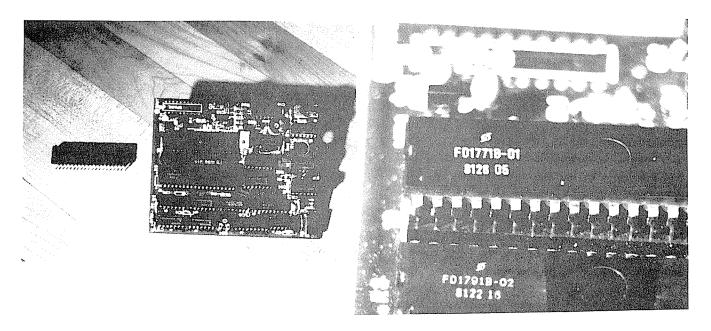

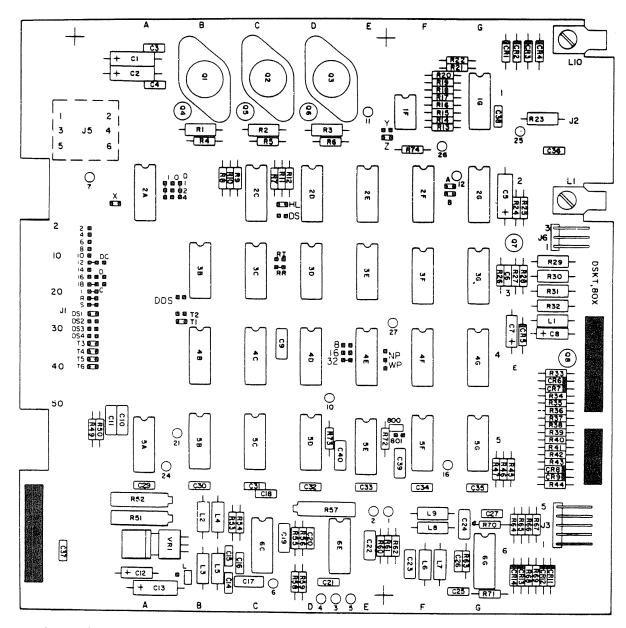

Refer to the following photographs to identify your type of expansion interface. There are two different designs from Tandy , the one on the left was their original interface, hence "OLD" and the one on the left is the newer of their designs and we refer to it as "NEW". Proceed to instructions provided for the type of interface which you own.

#### OLD EXPANSION INTERFACE

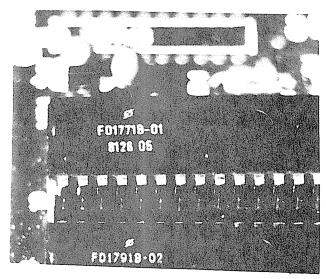

Observe the location of the floppy controller IC (the large black IC with 40 pins marked FD1771) located at position Z34. Note that the "notch" on the IC faces the center of the circuit board.

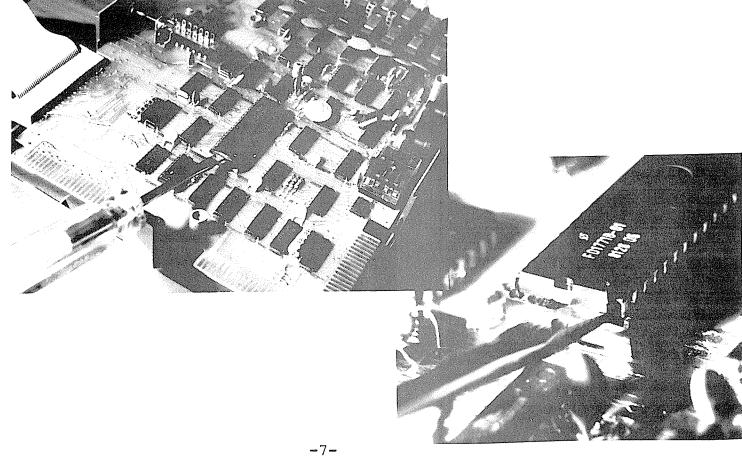

Carefully remove the the FD1771 by inserting the small screwdriver between the FD1771 and the socket that it is installed in, and pry it gently on each side. Refer to the following photos.

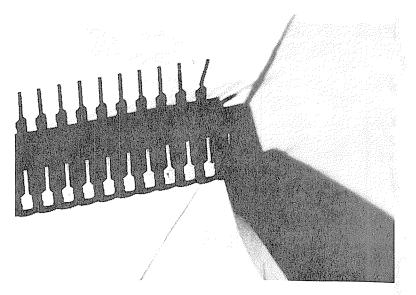

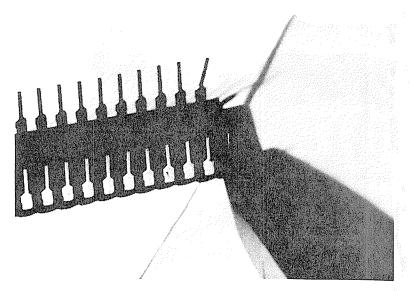

Should a lead become bent as in the next photo, use the pair of needle nose pliers or tweezers to carefully bend the pins back in place. Do not use excessive force or bend the lead back and forth too many times as the leads are delicate and can easily break.

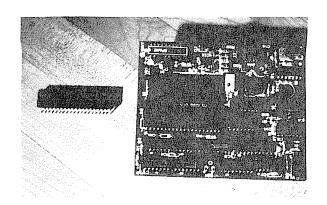

Now install the FD1771 in the socket (ICl0) provided on the LNDOUBLER 5/8.

Use extreme care to insure that all 40 pins seat properly into the socket. The notch on the FD1771 should face the outside of the LNDOUBLER 5/8.

Inspect the seating of the FD1771 in its socket by holding the LNDOUBLER 5/8 board with the notch side of the 1771 facing you. Look between the bottom of the IC and the top of the socket and inspect the two rows of pins of the IC. If a pin is bent, carefully remove the FD1771 and bend the lead straight with the needle nose pliers or the tweezers. Reinstall the FD1771 into the socket.

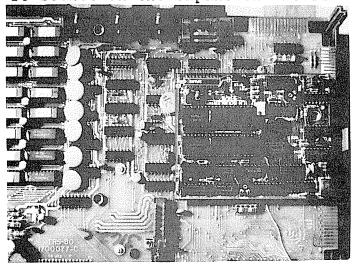

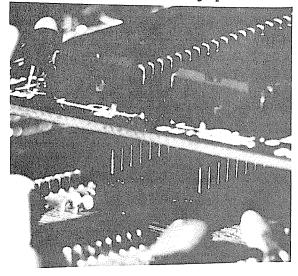

Prepare to install the LNDOUBLER 5/8 by inspecting the area on the interface near the socket and observe the area for components which might obstruct installation. Carefully reposition any components. Remove the protective foam block on the pins of the LNDOUBLER 5/8. Position the LNDOUBLER 5/8 above the socket and guide the pins of the LNDOUBLER 5/8 into the socket. Refer to the following photo.

Note that there is a small round hole on the LNDOUBLER 5/8 which allows a support on the expansion interface case to fit through.

Gently press the LNDOUBLER 5/8 into the socket. Now inspect the installation of the LNDOUBLER 5/8 making sure that all the pins are seated in the socket. If the LNDOUBLER 5/8 will not seat properly due to obstruction by a component which cannot be repositioned easily, it may be necessary to RAISE the LNDOUBLER 5/8 in its socket. This can be accomplished by installing a 40 pin dip IC socket between the LNDOUBLER 5/8 pins and the IC socket on the expansion interface.

Before closing up, note the switch on the outside corner of the LNDOUBLER 5/8. It is accesible from the outside of the interface, but you must make sure you know what position it is set to before closing up the interface. SET THE SWITCH TO THE "5" POSITION. A detailed explanation of the operation of this switch is included in a later section of this manual.

Now carefully position the case bottom panel over the interface, guiding the 6 screws into their 6 plastic supports on the case. Tighten the 6 screws completely.

Observe the opening in the interface that the 5/8 switch is visible. Using some sort of label or tape, mark the outside of the case in such a way as to identify the setting of the switch for the "5" position. Proceed to the section entitled "POWERING UP FOR THE FIRST TIME".

#### NEW EXPANSION INTERFACE

Note the location of the floppy controller IC (FD1771), the large black 40 pin IC at location Z42. The notch on the FD1771 should face Z41 and the connector for the Floppy disk drives.

Carefully remove the the FD1771 by inserting the small screwdriver between the FD1771 and the socket that it is installed in, and pry it gently on each side. Refer to the following photos.

Should a lead become bent as in the next photo, use the pair of needle nose pliers or tweezers to carefully bend the pins back in place. Do not use excessive force or bend the lead back and forth too many times as the leads are delicate and can easily break.

Now install the FD1771 in the socket (IC10) provided on the LNDOUBLER 5/8.

Use extreme care to insure that all 40 pins seat properly into the socket. The notch on the FD1771 should face the outside of the LNDOUBLER 5/8.

Inspect the seating of the FD1771 in its socket by holding the LNDOUBLER 5/8 board with the notch side of the 1771 facing you. Look between the bottom of the IC and the top of the socket and inspect the two rows of pins of the IC. If a pin is bent, carefully remove the FD1771 and bend the lead straight with the needle nose pliers or the tweezers. Reinstall the FD1771 into the socket.

Prepare to install the LNDOUBLER 5/8 by inspecting the area on the interface near the socket and observe the area for components which might obstruct installation. Carefully reposition any components. Remove the protective foam block on the pins of the LNDOUBLER 5/8. Position the LNDOUBLER 5/8 above the socket and guide the pins of the LNDOUBLER 5/8 into the socket. Refer to the following photo.

Gently press the LNDOUBLER 5/8 into the socket. Now inspect the installation of the LNDOUBLER 5/8 making sure that all the pins are seated in the socket. If the LNDOUBLER 5/8 will not seat properly due to obstruction by a component which cannot be repositioned easily, it may be necessary to RAISE the LNDOUBLER 5/8 in its socket. This can be accomplished by installing a 40 pin dip IC socket between the LNDOUBLER 5/8 pins and the IC socket on the expansion interface.

Before closing up, note the switch on the outside corner of the LNDOUBLER 5/8. It is accesible from the outside of the interface, but you must make sure you know what position it is set to before closing up the interface. SET THE SWITCH TO THE "5" POSITION. A detailed explanation of the operation of this switch is included in a later section of this manual.

Now carefully position the case bottom panel over the interface, guiding the 6 screws into their 6 plastic supports on the case. Tighten the 6 screws completely.

Observe the opening in the interface that the 5/8 switch is visible. Using some sort of label or tape, mark the outside of the case in such a way as to identify the setting of the switch for the "5" position. Proceed to the section entitled "POWERING UP FOR THE FIRST TIME".

#### LNW SYSTEM EXPANSION (ASSEMBLED)

Remove the two top mounting and two bottom mounting screws which secure the case top to the SYSTEM EXPANSION base. Remove the case top gently, noting that the front panel LED pilot lamp is wired to the system expansion circuit board. Position the case top upside down beside the chassis base. Remove the four circuit board mounting screws located on the edges of the system expansion circuit board. Gently position the circuit board component side up and remove the polarized power supply connector at Jl (near the large capacitors). Remove the circuit board away from the chassis and set it down on the inside of the top panel with the component side up. Since the component leads are sharp, handle the board with care and only by the edges. Also do not set the board down on any delicate surface or furniture as scratches will result.

Note the location of the floppy controller IC at Ul4. The "notch" on the 1771 should face C22 or the inside of the circuit board. See below:

Carefully remove the the FD1771 by inserting the small screwdriver between the FD1771 and the socket that it is installed in, and pry it gently on each side. Refer to the following photo.

Should a lead become bent as in the next photo, use the pair of needle nose pliers or tweezers to carefully bend the pins back in place. Do not use excessive force or bend the lead back and forth too many times as the leads are delicate and can easily break.

Now install the FD1771 in the socket (IC10) provided on the LNDOUBLER 5/8.

Use extreme care to insure that all 40 pins seat properly into the socket. The notch on the FD1771 should face the outside of the LNDOUBLER 5/8.

Inspect the seating of the FD1771 in its socket by holding the LNDOUBLER 5/8 board with the notch side of the 1771 facing you. Look between the bottom of the IC and the top of the socket and inspect the two rows of pins of the IC. If a pin is bent, carefully remove the FD1771 and bend the lead straight with the needle nose pliers or the tweezers. Reinstall the FD1771 into the socket.

Prepare to install the LNDOUBLER 5/8 by inspecting the area on the interface near the socket and observe the area for components which might obstruct installation. Carefully reposition any components. Remove the protective foam block on the pins of the LNDOUBLER 5/8. Position the LNDOUBLER 5/8 above the socket and guide the pins of the LNDOUBLER 5/8 into the socket. Refer to the following photo.

Gently press the LNDOUBLER 5/8 into the socket. Now inspect the installation of the LNDOUBLER 5/8 making sure that all the pins are seated in the socket. If the LNDOUBLER 5/8 will not seat properly due to obstruction by a component which cannot be repositioned easily, it may be necessary to RAISE the LNDOUBLER 5/8 in its socket. This can be accomplished by installing a 40 pin dip IC socket between the LNDOUBLER 5/8 pins and the IC socket on the expansion interface.

Before closing up, note the switch on the outside corner of the LNDOUBLER 5/8. It is accesible from the outside of the interface, but you must make sure you know what position it is set to before closing up the interface. SET THE SWITCH TO THE "5" POSITION. A detailed explanation of the operation of this switch is included in a later section of this manual.

Reconnect the power supply connector at Jl noting that the correct way to connect Jl is such that the connector "locks" in place. Position the circuit board back in place with the component side down. Reinstall the four circuit board mounting screws. Note that their should be three screws with washers and one without. The one without is the one closest to the RS232 BAUD rate configuration area. Position the case top back on top of the chassis, install the top and bottom support screws.

Observe the opening in the interface that the 5/8 switch is visible. Using some sort of label or tape, mark the outside of the case in such a way as to identify the setting of the switch for the "5" position. Proceed to the section entitled "POWERING UP FOR THE FIRST TIME".

#### LNW SYSTEM EXPANSION (KIT FORM)

Follow the instructions as for the assembled and test unit but it WILL be necessary to obtain and install a 40 pin dip IC socket as a spacer between the LNDOUBLER 5/8 and the interface socket if sockets were used in any of the IC's surrounding U14.

#### POWERING UP FOR THE FIRST TIME

#### CAUTION

DO NOT INSTALL A DOUBLE DENSITY SYSTEM DISK INTO THE DISK DRIVE AT THIS TIME!!! PROPER OPERATION UNDER SINGLE DENSITY MUST BE ESTABLISHED PRIOR TO ATTEMPTING TO BOOT THE DOUBLE DENSITY (DOSPLUS) SYSTEM DISK. INSTALLING YOUR ONLY COPY OF A DOUBLE DENSITY SYSTEM DISK WHEN PROPER INSTALLATION HAS NOT BEEN ESTABLISHED MAY LEAD TO NEEDLESS FRUSTRATION AND DELAY

Reconnect power, your cpu (keyboard), and floppy cable to your interface. Do not connect a printer or RS232 cable until proper operation has been established below.

Power your drives, the interface, and insert the SINGLE DENSITY SYSTEM DISK that you created while testing your interface into your drive  $\emptyset$ .

Turn on the CPU

If the SINGLE DENSITY disk boots correctly, replace the single density system disk with the DOUBLE DENSITY system disk.

Reset the CPU

If the disk boots correctly, proceed to make a backup of the Double density system disk. If it backs up correctly, proceed to reconnect the rest of your peripherals and enjoy the most reliable double density operation possible! If any problems occur, turn the system off and proceed to the section of the manual entitled "TROUBLESHOOTING".

#### CONNECTING EIGHT INCH DISK DRIVES

Eight inch disk drives which are SHUGART compatible can easily be connected to an expansion interface or SYSTEM EXPANSION with the LNDOUBLER 5/8 installed. A special cable adaptor board which converts the 34 conductor 5.25" floppy cable to the 50 conductor 8" drive cable is available from LNW RESEARCH CORPORATION ,stk#1096. One end of the adaptor board plugs into your 5" drive cable (cable with no pins pulled) and the other end of the adaptor plugs into your 8" drive cable, thus interfacing the 8" drive(s) to your system. The adaptor board also has a connection for the "TG43" or write current line which may be needed if your 8" drive requires it. If it is needed , it may be ordered from LNW. The 8" drive , 4-diskcable is also available from LNW. Since all 8" disk drives are not the same compare the following chart with the pinouts for the drive that you plan to be using. The following chart also shows the simularities between the 5" and 8" disk drive interface lines.

| PIN #<br>5"                                                                          | SIGNAL                                                                                    | PIN # 8" SIGNAL 2-ground (write current) 4-not used 6-not used 8-not used 10-two sided (not used) 12-disk change (not used) 14-side select 16-activity indicator                                                            |

|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12-driv<br>14-driv<br>16-moto<br>18-diro<br>20-step<br>22-wriv<br>24-wriv<br>26-trac | used used ex ve select 1 ve select 2 ve select 3 or on ection select te data te gate ck Ø | 16-activity indicator 18-head load (not used) 20-index 22-ready (not used) 24-not used 26-drive select 1 28-drive select 2 30-drive select 3 32-motor on 34-direction select 36-step 38-write data 40-write gate 42-track 0 |

| 30-read                                                                              | ve select 4/side select                                                                   | 44-write protect<br>46-read data<br>48-not used<br>50-not used                                                                                                                                                              |

#### WAIT STATE CABLE

If you intend to run operating systems other than DOSPLUS 3.38 and NEWDOS8Ø 2.Ø with 8" drive support, you may need the special "WAIT CABLE" wired from the "wait pin" on the LNDOUBLER 5/8 to pin 33 of the screen printer bus. This line causes the CPU to wait in order to pick up the data correctly while doing disk I/O. Since improvements have been made in the operating systems as far as the disk I/O is concerned, it has been found that the 1.77mhz cpu speed is adequate to handle the data rate of the 8" disk drive without any special hardware. Hopefully the operating systems which have in the past required this logic, will rewrite their disk I/O routines to eliminate this unnecesary cable. The "WAIT CABLE" IS AVAILABLE from LNW RESEARCH. Order information is included in the rear of this manual.

#### EIGHT INCH DISK DRIVE OPERATION

If you want to use 8" disk drives, either mixed with 5" drives or only with 8" drives make sure that 5" operation is assured. After connecting the 8" disk drive to your system as described , attempt to format an 8" disk drive. If it formats correctly, flip the 5/8 switch in the rear and boot an 8" system disk, reconfiguring your drives so as to have an 8" drive at drive Ø. If it works, set up your drives and the 5/8 switch as you would like and enjoy the increased density and reliability of eight inch disk drives! If problems result, consult the section in the manual entitled "TROUBLESHOOTING".

#### INSTALLING A SPEED UP KIT IN YOUR TRS80

Changing the speed of the CPU in a TRS80 involves more than just changing the Z80 to a Z80A. It involves soldering, wiring and a comprehensive plan to obtain the correct timing for the 4116 memory components in the INTERFACE as well as in the CPU. The speed up kit required to run 8" double density must be at least twice the standard speed, and MUST NOT return to the slow speed under disk I/O. One such speed up kit is available from :

ARCHBOLD ELECTRONICS 10708 Segovia Way Rancho Cordova CA 95670

We do not recommend such a speed up kit for someone who does not have a certain degree of technical skill in electronics and is proficient in soldering.

For further details concerning the installation of speed up kits and other modifications to the TRS80 we recommend the following book:

THE CUSTOM TRS80 and other mysteries by Dennis Kitsz available from- IJG COMPUTER SERVICES 1260 West Foothill blvd Upland CA 91786

#### TROUBLESHOOTING

We have included a list of symptoms and possible solutions to aid in the search for your problem. Most common problems occur from hasty late night installations. Try everything imaginable before coming to the conclusion that LNDOUBLER 5/8 is at fault. We will be glad to assist you in problems concerning the installation of the LNDOUBLER 5/8. We cannot help you with custom installations nor can we install your LNDOUBLER 5/8 for you. We cannot help you in determining if your 8" disk drive will work with the LNDOUBLER 5/8 nor can we recommend ways to modify 8" disk drives which are not SHUGART compatible. If you are having problems with configuring your 8" disk drive, contact the manufacturer or dealer that sold the drive.We cannot help you with problems related to your 8" drives unless you are using the cables and cable adaptors which WE manufacture! We will not talk to you about wiring the LNDOUBLER 5/8 to other computers or other interfaces. ( ie. MOD III or PMC80)

#### HERE ARE SOME OF THE COMMON PROBLEMS

SYMPTOM: Single density DOS disk won't boot. Motor turns on, drive light turns on...then turns off.

#### PROBABLE CAUSE:

- 1. 5/8 switch set to 8" position

- 2. Defective single density disk

- 3. Improper power up procedure, power up again

- 4. FD1771 improperly installed in LNDOUBLER 5/8

- 5. Improper installation of the LNDOUBLER 5/8

SYMPTOM: Nothing happens on power up .Computer displays "memory size?" or similar message.

#### PROBABLE CAUSE:

- 1. Expansion interface not powered up

- 2. LNDOUBLER 5/8 improperly installed

SYMPTOM: Single density disk boots but double density operating system disk will not boot or does not function.

#### PROBABLE CAUSE:

- 1. Defective double density system disk...Contact your dealer about receiving a new copy.

- 2. Improper termination of your disk drives.

SYMPTOM: Single and Double density disks boot correctly but will not backup or write to disk in any density.

#### PROBABLE CAUSE:

- l. More than one disk drive with termination resistors installed.Last disk drive on cable should have the termination resistor packs.

- 2. Improper installation of LNDOUBLER 5/8 (may have a pin on the doubler bent)

- 3. Defective FD1771 IC

SYMPTOM: Double density operation is correct but will not format, backup or write to disk correctly in single density.

#### PROBABLE CAUSE:

- 1. Improper installation of FD1771

- 2. Defective FD1771

SYMPTOM: 5" single and double density operation is correct, but 8" drives will not function.

#### PROBABLE CAUSE:

- 1. Improper configuration of 8" disk drive

- 2. Improper termination of 8" disk drive

- 3. 8" disk drive cabling defective

- 4. Configuration of 8" disk drive wrong

SYMPTOM: 8" disk drive operation in single density is correct but double density 8" will not work.

#### PROBABLE CAUSE:

- l.Attempting to run 8" double density on an unmodified TRS-80 (1.77 mhz CPU speed)

- 2. Speed up kit forces low cpu speed (1.77 mhz) during disk I/O

- 3.Speed up kit does not bring the CPU up to 3.55 mhz

SYMPTOM: 8" single density will not operate under OMIKRON CP/M or NEWDOS80 1.0.

#### PROBABLE CAUSE:

1. "WAIT CABLE" not installed between LNDOUBLER 5/8 and pin 33 of the screen printer bus.

SYMPTOM: DOSPLUS 3.3 will not boot

#### PROBABLE CAUSE:

1. The original DOSPLUS 3.3d is NOT compatible with the LNDOUBLER 5/8 in ANY FORM, although DOSPLUS 3.2d is compatible in double density with 5" drives only.Although you cannot boot, or use any of the utilities of the DOSPLUS 3.3d you can copy or transfer all your programs or data from the 3.3 disk to your new 3.38 system disk.

SYMPTOM: Problems occur in double density 8" in the upper tracks.

#### PROBABLE CAUSE:

- 1. Above track 43 the write current must be lowered on some 8" disk drives. If the drive you have has a signal called "write current switch" then the "TG43" cable must be installed between the LNDOUBLER 5/8 and the 8" disk adaptor board.

- 2. Diskettes not rated for double density operation

SYMPTOM: When attempting to write on a 8" disk, the DOS error indicates that the disk is "WRITE PROTECTED".

#### PROBABLE CAUSE:

1.8" disk drives have the opposite convention for WRITE PROTECT. The write protect tab must be installed IN ORDER TO WRITE ON THE DISK.

#### RETURNING YOUR LNDOUBLER 5/8 FOR REPAIR

If you cannot get your LNDOUBLER 5/8 to function properly within the warranty period, you may elect to return the LNDOUBLER 5/8 to your dealer for replacement (usually the fastest remedy) or you may return it to the factory for repair(provided you filled out the warranty registration and provide proof of purchase from an authorized dealer of LNW RESEARCH CORPORATION). Give our Service Department a call before returning it so a technician can try and help you over the phone. If the LNDOUBLER 5/8 is out of warranty then call the factory and return the defective unit for repair. Service rates will be given to you over the phone at the time you call.

When returning anything to the factory for repair be sure to:

1. Pack it properly with plenty of padding

NOME

- 2. Ship it prepaid UPS or Insured PARCEL POST

- 3. Enclose a complete description of the problem

- 4. Warranty units should include PROOF OF PURCHASE

| NOTE                                                                            |               |               | _      |

|---------------------------------------------------------------------------------|---------------|---------------|--------|

| Problems concerning the diskette supplied with updates should be direct system. | the LNDOUBLER | 8.5/8 as well | as its |

#### THEORY OF OPERATION

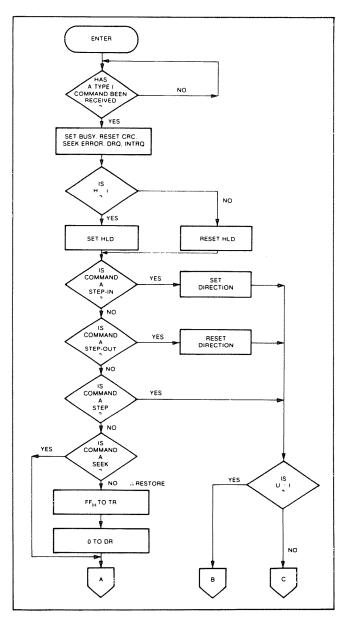

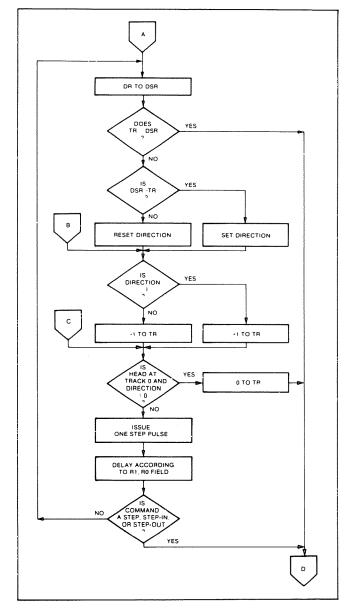

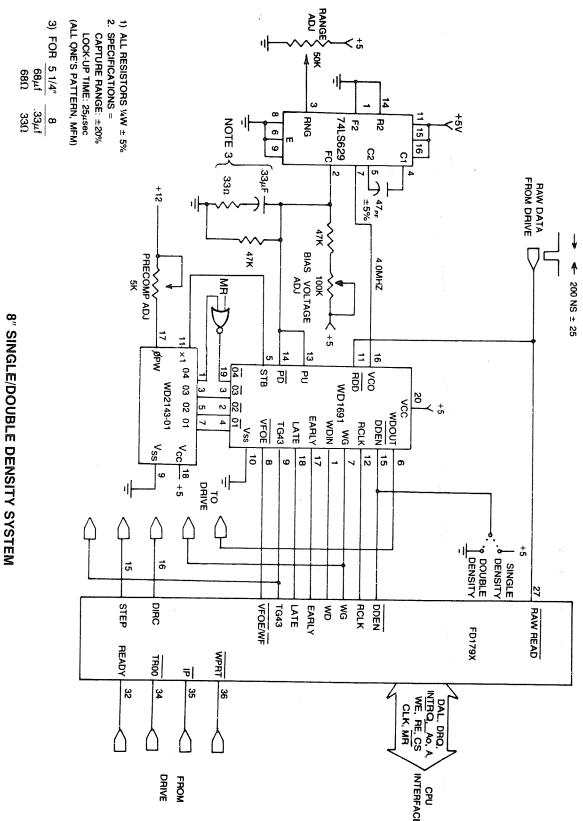

The LNDOUBLER 5/8 has as it's heart two floppy controller IC's— the FD1771 (single density controller) and the FD1791 (single and double). The reason that the 1771 is still needed when the 1791 can do single density operation is that the commands are slightly different and the BOOT in the level 2 ROMs would not work. And since we want to stay 100% software compatible we keep the FD1771. The two floppy controller IC's are tied together so only one of the two can be enabled at one time.We turn on the 1771 when we do single density disk I/O and we enable the 1791 for double density operation.

To switch from 5.25" disk drives to 8" inch disk drives we

To switch from 5.25" disk drives to 8" inch disk drives we must change the frequency of the clock going into the 1771 and 1791 and do some other switching of signals. A software switch is also provided for this. In addition there exists some special "wait state logic" which allows 8" disk drive operation under a slow CPU speed. This logic is used by several operating systems and is maintained for compatibility reasons. It may also be found that this logic can be used for 8" double density operation with a 1.77mhz cpu speed.

The software switch locations are summarized in the chart below:

| WRITE TO PORT | WITH DATA                                |

|---------------|------------------------------------------|

| 37EC (H)      | FF (H)                                   |

| 37EC          | FE                                       |

| 37EE          | CØ                                       |

| 37EE          | AØ                                       |

| 37EE          | ΕØ                                       |

| 37EE          | CØ                                       |

|               | 37EC (H)<br>37EC<br>37EE<br>37EE<br>37EE |

Whenever any switching is done the floppy controller which is NOW enabled is initialized and all the internal registers restored. Refer to the data sheets supplied in the back of this section for programming information concerning the floppy controller IC's. Although the "wait" logic need not be invoked for single density operation for 8" drives at the 1.77mhz CPU speed an explanation of it's operation follows—

- 1. The wait state logic is turned on

- 2. The floppy controller is initialized and the registers set

- 3. The command is given to floppy controller to read or write.

- 4. The status register is read. This causes the wait state logic to issue a "wait" to the Z80 CPU UNTIL:

- a. the busy bit in the status register goes false

- or b. DRQ on the floppy controller chip goes true

- or c. IRQ on the floppy controller chip goes true

If the condition that removed the wait was (a.) or (b.) above then the wait state logic is still "on" but the CPU wait was only removed until the next time the status register of

the floppy controller is read. If the condition that removed the wait was (c.) then the wait state logic is turned "off" .

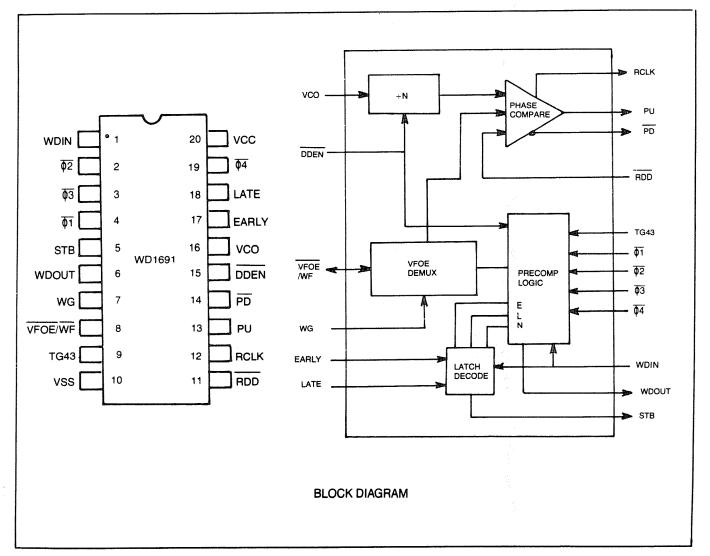

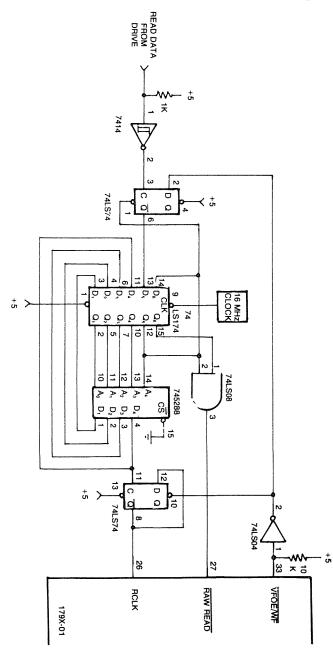

#### ANALOG PHASE LOCK LOOP DATA SEPARATION

The VCO -the voltage controlled oscillator a 74LS629 at IC15 generates the 4mhz VCO frequency (2mhz for 5.25" disk drive operation) for the WD1691 the floppy support logic IC(at IC8). In order to guarantee that it is not sensitive to power supply variations from interface to interface, VR1 (78LØ5) provides a regulated supply to the 74LS629 and the adjustment controls R25 and R26. The 74LS629 is an improved version of the 74S124 providing excellent immunity to temperature variation and aging. R25 is a multiturn pot to adjust the frequency range and R26 adjusts the bias voltage (for a stable "free running" frequency) for the VCO. The WD1691 and the 74LS629 make up the ANALOG PHASE LOCK LOOP DATA SEPARATION.

#### PRECISION WRITE PRECOMPENSATION

The WD2143 provides an accurate write precompensation value according to the adjustment of R24. A negative true pulse of the actual precompensation value can be observed with an oscilloscope at IC8 pin 4. Write precompensation is factory aligned to 200 ns +-25ns and is enabled only for double density operation (all tracks 5.25" and tracks above 43 for 8"). The interface between the WD 2143 and the WD1691 is explained in some detail in the data sheets supplied. Schematics and further details are beyond the scope of this manual.

#### 5/8 SWITCH

On powerup or reset, the LNDOUBLER 5/8 switches to 5.25" or 8" drive operation depending on the setting of the 5/8 switch. Since the LNDOUBLER 5/8 always powers up in single density for compatibility reasons, the system disk must always have a single density boot at track Ø, sector Ø. This applys also to double density 8" system disks.Note that data disks are not required to have any single density tracks.

#### DATA SHEETS

The following data sheets are provided for those interested in the technical details concerning the FD1791,WD1691, and the WD2143. The data sheets have been edited to conserve space and we are not distributing the unedited data sheets. The data sheets are reprinted with the permission of WESTERN DIGITAL CORPORATION. Write precompensation is thoroughly discussed as well as the relative performance of the phase lock loop and the rom programmed counter type data separation design techniques.

For those interested in more details concerning how to program the floppy controller IC's in your computer ,the following book is recommended:

TRS-80 MODEL I DISK INTERFACING by William Barden Jr. available from - 80-US Journal (206) 475-2219

## Western digital

### FD 179X-02 Floppy Disk Formatter/Controller Family

#### **FEATURES**

- TWO VFO CONTROL SIGNALS

- SOFT SECTOR FORMAT COMPATIBILITY

- **AUTOMATIC TRACK SEEK WITH** VERIFICATION

- ACCOMMODATES SINGLE AND DOUBLE **DENSITY FORMATS** IBM 3740 Single Density (FM) IBM System 34 Double Density (MFM)

- READ MODE

- Single/Multiple Sector Read with Automatic Search or Entire Track Read

- Selectable 128 Byte or Variable length Sector

- WRITE MODE

- Single/Multiple Sector Write with Automatic Sector Search

- Entire Track Write for Diskette Formatting

- SYSTEM COMPATIBILITY Double Buffering of Data 8 Bit Bi-Directional Bus for Data, Control and Status DMA or Programmed Data Transfers All Inputs and Outputs are TTL Compatible

- On-Chip Track and Sector Registers/Comprehensive Status Information

- PROGRAMMABLE CONTROLS Selectable Track to Track Stepping Time Side Select Compare

- WRITE PRECOMPENSATION

- WINDOW EXTENSION

- INCORPORATES ENCODING/DECODING AND ADDRESS MARK CIRCUITRY

- FD1792/4 IS SINGLE DENSITY ONLY

- FD1795/7 HAS A SIDE SELECT OUTPUT

#### 179X-02 FAMILY CHARACTERISTICS

| FEATURES              | 1791 | 1793 | 1795 | 1797 |

|-----------------------|------|------|------|------|

| Single Density (FM)   | Х    | Х    | Х    | Х    |

| Double Density (MFM)  | Х    | Х    | Х    | Х    |

| True Data Bus         |      | Х    |      | Х    |

| Inverted Data Bus     | Χ    |      | Х    |      |

| Write Precomp         | Х    | Х    | Х    | X    |

| Side Selection Output |      |      | Х    | Х    |

#### **APPLICATIONS**

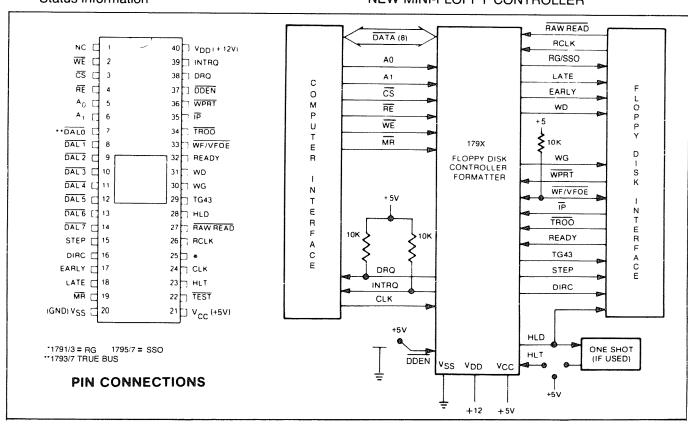

FLOPPY DISK DRIVE INTERFACE SINGLE OR MULTIPLE DRIVE CONTROLLER/ **FORMATTER NEW MINI-FLOPPY CONTROLLER**

FD179X SYSTEM BLOCK DIAGRAM

#### **GENERAL DESCRIPTION**

The FD179X are MOS LSI devices which perform the functions of a Floppy Disk Formatter/Controller in a single chip implementation. The FD179X, which can be considered the end result of both the FD1771 and FD1781 designs, is IBM 3740 compatible in single density mode (FM) and System 34 compatible in Double Density Mode (MFM). The FD179X contains all the features of its predecessor the FD1771, plus the added features necessary to read/write and format a double density diskette. These include address mark detection, FM and MFM encode and decode logic, window extension, and write precompensation. In order to maintain compatibility, the FD1771, FD1781, and FD179X designs were made as close as possible with the computer interface, instruction set, and I/O registers being identical. Also, head load

control is identical. In each case, the actual pin assignments vary by only a few pins from any one to another.

The processor interface consists of an 8-bit bidirectional bus for data, status, and control word transfers. The FD179X is set up to operate on a multiplexed bus with other bus-oriented devices.

The FD179X is fabricated in N-channel Silicon Gate MOS technology and is TTL compatible on all inputs and outputs. The 1793 is identical to the 1791 except the DAL lines are TRUE for systems that utilize true data busses.

The 1795/7 has a side select output for controlling double sided drives, and the 1792 and 1794 are "Single Density Only" versions of the 1791 and 1793. On these devices, DDEN must be left open.

#### **PIN OUTS**

| PIN<br>NUMBER | PIN NAME                 | SYMBOL        | FUNCTION                                                                                                                                                                                                                                                                                                                   |

|---------------|--------------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | NO CONNECTION            | NC            | Pin 1 is internally connected to a back bias generator and must be left open by the user.                                                                                                                                                                                                                                  |

| 19            | MASTER RESET             | MR            | A logic low on this input resets the device and loads HEX 03 into the command register. The Not Ready (Status Bit 7) is reset during MR ACTIVE. When MR is brought to a logic high a RESTORE Command is executed, regardless of the state of the Ready signal from the drive. Also, HEX 01 is loaded into sector register. |

| 20            | POWER SUPPLIES           | Vss           | Ground                                                                                                                                                                                                                                                                                                                     |

| 21            |                          | Vcc           | +5V ±5%                                                                                                                                                                                                                                                                                                                    |

| 40            |                          | VDD           | +12V ±5%                                                                                                                                                                                                                                                                                                                   |

| COMPUTER      | INTERFACE:               |               |                                                                                                                                                                                                                                                                                                                            |

| 2             | WRITE ENABLE             | WE            | A logic low on this input gates data on the DAL into the selected register when CS is low.                                                                                                                                                                                                                                 |

| 3             | CHIP SELECT              | <del>CS</del> | A logic low on this input selects the chip and enables computer communication with the device.                                                                                                                                                                                                                             |

| 4             | READ ENABLE              | RE            | A logic low on this input controls the placement of data from a selected register on the DAL when $\overline{\text{CS}}$ is low.                                                                                                                                                                                           |

| 5,6           | REGISTER SELECT<br>LINES | A0, A1        | These inputs select the register to receive/ transfer data on the DAL lines under RE and WE control:  A1 A0 RE WE                                                                                                                                                                                                          |

|               |                          |               | A1 A0 RE WE  0 0 Status Reg Command Reg  0 1 Track Reg Track Reg  1 0 Sector Reg Sector Reg  1 1 Data Reg Data Reg                                                                                                                                                                                                         |

| 7-14          | DATA ACCESS LINES        | DAL0-DAL7     | Eight bit inverted Bidirectional bus used for transfer of data, control, and status. This bus is receiver enabled by WE or transmitter enabled by RE.                                                                                                                                                                      |

| 24            | CLOCK                    | CLK           | This input requires a free-running square wave clock for internal timing reference, 2 MHz for 8" drives, 1 MHz for mini-drives.                                                                                                                                                                                            |

| PIN<br>NUMBER | PIN NAME                           | SYMBOL      | PHARMAN                                                                                                                                                                                                                                                                                                                              |

|---------------|------------------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 38            | DATA REQUEST                       | <del></del> | FUNCTION                                                                                                                                                                                                                                                                                                                             |

|               | DATA NEGOEST                       | DRQ         | This open drain output indicates that the DR contains assembled data in Read operations, or the DR is empty in Write operations. This signal is reset when serviced by the computer through reading or loading the DR in Read or Write operations, respectively. Use 10K pull-up resistor to +5.                                     |

| 39            | INTERRUPT<br>REQUEST               | INTRQ       | This open drain output is set at the completion of any command and is reset when the STATUS register is                                                                                                                                                                                                                              |

| FLOPPY DI     | SK INTERFACE:                      |             | read or the command register is written to. Use 10K pull-up resistor to +5.                                                                                                                                                                                                                                                          |

| 15            | STEP                               | STEP        | The step output contains a pulse for each step.                                                                                                                                                                                                                                                                                      |

| 16            | DIRECTION                          | DIRC        | Direction Output is active high when stepping in, active low when stepping out.                                                                                                                                                                                                                                                      |

| 17            | EARLY                              | EARLY       | Indicates that the WRITE DATA pulse occurring while Early is active (high) should be shifted early for write precompensation.                                                                                                                                                                                                        |

| 18            | LATE                               | LATE        | Indicates that the write data pulse occurring while Late is active (high) should be shifted late for write precompensation.                                                                                                                                                                                                          |

| 22            | TEST                               | TEST        | This input is used for testing purposes only and should be tied to +5V or left open by the user unless interfacing to voice coil actuated motors.                                                                                                                                                                                    |

| 23            | HEAD LOAD TIMING                   | HLT         | When a logic high is found on the HLT input the head is assumed to be engaged.                                                                                                                                                                                                                                                       |

| 25            | READ GATE (1791/3)                 | RG          | A high level on this output indicates to the data separator circuitry that a field of zeros (or ones) has been encountered, and is used for synchronization.                                                                                                                                                                         |

| 25            | SIDE SELECT OUTPUT<br>(1795, 1797) | SSO         | The logic level of the Side Select Output is directly controlled by the 'S' flag in Type II or III commands. When S = 1, SSO is set to a logic 1. When S = 0, SSO is set to a logic 0. The Side Select Output is only updated at the beginning of a Type II or III command. It is forced to a logic 0 upon a MASTER RESET condition. |

| 26            | READ CLOCK                         | RCLK        | A nominal square-wave clock signal derived from the data stream must be provided to this input. Phasing (i.e. RCLK transitions) relative to RAW READ is important but polarity (RCLK high or low) is not.                                                                                                                            |

| 27            | RAW READ                           | RAW READ    | The data input signal directly from the drive. This input shall be a negative pulse for each recorded flux transition.                                                                                                                                                                                                               |

| 28            | HEAD LOAD                          | HLD         | The HLD output controls the loading of the Read-Write head against the media.                                                                                                                                                                                                                                                        |

| 29            | TRACK GREATER<br>THAN 43           | TG43        | This output informs the drive that the Read/Write head is positioned between tracks 44-76. This output is valid only during Read and Write Commands.                                                                                                                                                                                 |

| 30            | WRITE GATE                         | WG          | This output is made valid before writing is to be performed on the diskette.                                                                                                                                                                                                                                                         |

| PIN<br>NUMBER | PIN NAME                  | SYMBOL  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------|---------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31            | WRITE DATA                | WD      | A 250 ns (MFM) or 500 ns (FM) pulse per flux transition. WD contains the unique Address marks as well as data and clock in both FM and MFM formats.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 32            | READY                     | READY   | This input indicates disk readiness and is sampled for a logic high before Read or Write commands are performed. If Ready is low the Read or Write operation is not performed and an interrupt is generated. Type I operations are performed regardless of the state of Ready. The Ready input appears in inverted format as Status Register bit 7.                                                                                                                                                                                                                                                                                                                                                                       |

| 33            | WRITE FAULT<br>VFO ENABLE | WF/VFOE | This is a bi-directional signal used to signify writing faults at the drive, and to enable the external PLO data separator. When WG = 1, Pin 33 functions as a WF input. If WF = 0, any write command will immediately be terminated. When WG = 0, Pin 33 functions as a VFOE output. VFOE will go low during a read operation after the head has loaded and settled (HLT = 1). On the 1795/7, it will remain low until the last bit of the second CRC byte in the ID field. VFOE will then go high until 8 bytes (MFM) or 4 bytes (FM) before the Address Mark. It will then go active until the last bit of the second CRC byte of the Data Field. On the 1791/3, VFOE will remain low until the end of the Data Field. |

| 34            | TRACK 00                  | TR00    | This input informs the FD179X that the Read/Write head is positioned over Track 00.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 35            | INDEX PULSE               | ĪP      | This input informs the FD179X when the index hole is encountered on the diskette.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 36            | WRITE PROTECT             | WPRT    | This input is sampled whenever a Write Command is received. A logic low terminates the command and sets the Write Protect Status bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 37            | DOUBLE DENSITY            | DDEN    | This pin selects either single or double density operation. When $\overline{DDEN}=0$ , double density is selected. When $\overline{DDEN}=1$ , single density is selected. This line must be left open on the 1792/4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

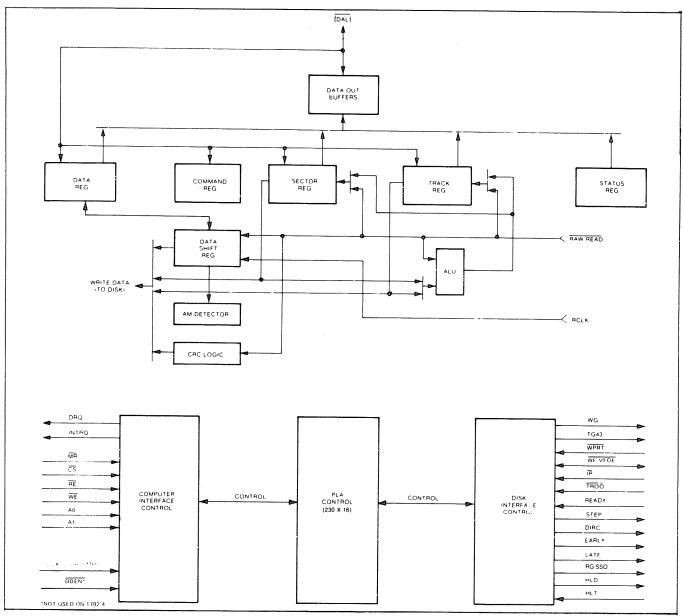

### **ORGANIZATION**

The Floppy Disk Formatter block diagram is illustrated on page 5. The primary sections include the parallel processor interface and the Floppy Disk interface.

**Data Shift Register**—This 8-bit register <u>assembles</u> serial data from the Read Data input (RAW READ) during Read operations and transfers serial data to the Write Data output during Write operations.

Data Register—This 8-bit register is used as a holding register during Disk Read and Write operations. In Disk Read operations the assembled data byte is transferred in parallel to the Data Register from the Data Shift Register. In Disk Write operations information is transferred in parallel from the Data Register to the Data Shift Register.

When executing the Seek command the Data Register holds the address of the desired Track position. This register is loaded from the DAL and gated onto the DAL under processor control.

Track Register—This 8-bit register holds the track number of the current Read/Write head position. It is incremented by one every time the head is stepped in (towards track 76) and decremented by one when the head is stepped out (towards track 00). The contents of the register are compared with the recorded track number in the ID field during disk Read, Write, and Verify operations. The Track Register can be loaded from or transferred to the DAL. This Register should not be loaded when the device is busy.

FD179X BLOCK DIAGRAM

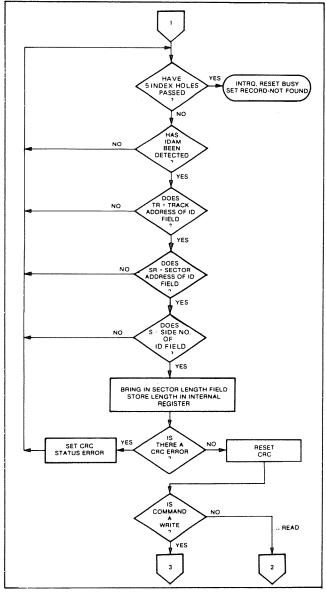

Sector Register (SR)—This 8-bit register holds the address of the desired sector position. The contents of the register are compared with the recorded sector number in the ID field during disk Read or Write operations. The Sector Register contents can be loaded from or transferred to the DAL. This register should not be loaded when the device is busy.

Command Register (CR)—This 8-bit register holds the command presently being executed. This register should not be loaded when the device is busy unless the new command is a force interrupt. The command register can be loaded from the DAL, but not read onto the DAL.

Status Register (STR)—This 8-bit register holds device Status information. The meaning of the Status bits is a function of the type of command previously executed. This register can be read onto the DAL, but not loaded from the DAL.

**CRC Logic**—This logic is used to check or to generate the 16-bit Cyclic Redundancy Check (CRC). The polynomial is:  $G(x) = x^{16} + x^{12} + x^5 + 1$ .

The CRC includes all information starting with the address mark and up to the CRC characters. The CRC register is preset to ones prior to data being shifted through the circuit.

**Arithmetic/Logic Unit (ALU)**—The ALU is a serial comparator, incrementer, and decrementer and is used for register modification and comparisons with the disk recorded ID field.

**Timing and Control**—All computer and Floppy Disk Interface controls are generated through this logic. The internal device timing is generated from an external crystal clock.

The FD1791/3 has two different modes of operation according to the state of  $\overline{DDEN}$ . When  $\overline{DDEN} = 0$  double density (MFM) is assumed. When  $\overline{DDEN} = 1$ , single density (FM) is assumed.

**AM Detector**—The address mark detector detects ID, data and index address marks during read and write operations.

### PROCESSOR INTERFACE

The interface to the processor is accomplished through the eight Data Access Lines (DAL) and associated control signals. The DAL are used to transfer Data, Status, and Control words out of, or into the FD179X. The DAL are three state buffers that are enabled as output drivers when Chip Select (CS) and Read Enable (RE) are active (low logic state) or act as input receivers when CS and Write Enable (WE) are active.

When transfer of data with the Floppy Disk Controller is required by the host processor, the device address is decoded and  $\overline{CS}$  is made low. The address bits A1 and A0, combined with the signals  $\overline{RE}$  during a Read operation or  $\overline{WE}$  during a Write operation are interpreted as selecting the following registers:

| A1- | A0_ | READ (RE)       | WRITE (WE)       |

|-----|-----|-----------------|------------------|

| 0   | 0   | Status Register | Command Register |

| 0   | 1   | Track Register  | Track Register   |

| 1   | 0   | Sector Register | Sector Register  |

| 1   | 1   | Data Register   | Data Register    |

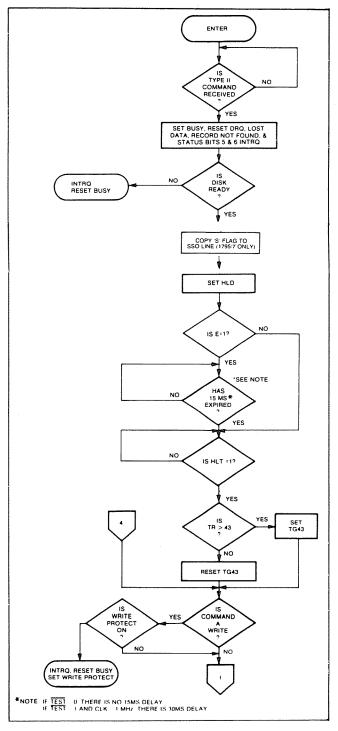

During Direct Memory Access (DMA) types of data transfers between the Data Register of the FD179X and the processor, the Data Request (DRQ) output is used in Data Transfer control. This signal also appears as status bit 1 during Read and Write operations.

On Disk Read operations the Data Request is activated (set high) when an assembled serial input byte is transferred in parallel to the Data Register. This bit is cleared when the Data Register is read by the processor. If the Data Register is read after one or more characters are lost, by having new data transferred into the register prior to processor readout, the Lost Data bit is set in the Status Register. The Read operation continues until the end of sector is reached.

On Disk Write operations the data Request is activated when the Data Register transfers its contents to the Data Shift Register, and requires a new data byte. It is reset when the Data Register is loaded with new data by the processor. If new data is not loaded at the time the next serial byte is required by the Floppy Disk, a byte of zeroes is written on the diskette and the Lost Data bit is set in the Status Register.

At the completion of every command an INTRQ is generated. INTRQ is reset by either reading the status register or by loading the command register with a new command. In addition, INTRQ is generated if a Force Interrupt command condition is met.

## FLOPPY DISK INTERFACE

The 179X has two modes of operation according to the state of  $\overline{DDEN}$  (Pin 37). When  $\overline{DDEN}=1$ , single density is selected. In either case, the CLK input (Pin 24) is at 2 MHz. However, when interfacing with the mini-floppy, the CLK input is set at 1 MHz for both single density and double density. When the clock is at 2 MHz, the stepping rates of 3, 6, 10, and 15 ms are obtainable. When CLK equals 1 MHz these times are doubled.

### **HEAD POSITIONING**

Five commands cause positioning of the Read-Write head (see Command Section). The period of each positioning step is specified by the r field in bits 1 and 0 of the command word. After the last directional step an additional 15 milliseconds of head settling time takes place if the Verify flag is set in Type I commands. Note that this time doubles to 30 ms for a 1 MHz clock. If TEST = 0, there is zero settling time. There is also a 15 ms head settling time if the E flag is set in any Type II or III command.

The rates (shown in Table 1) can be applied to a Step-Direction Motor through the device interface.

**Step**—A 2  $\mu$ s (MFM) or 4  $\mu$ s (FM) pulse is provided as an output to the drive. For every step pulse issued, the drive moves one track location in a direction determined by the direction output.

**Direction (DIRC)**—The Direction signal is active high when stepping in and low when stepping out. The Direction signal is valid 12  $\mu$ s before the first stepping pulse is generated.

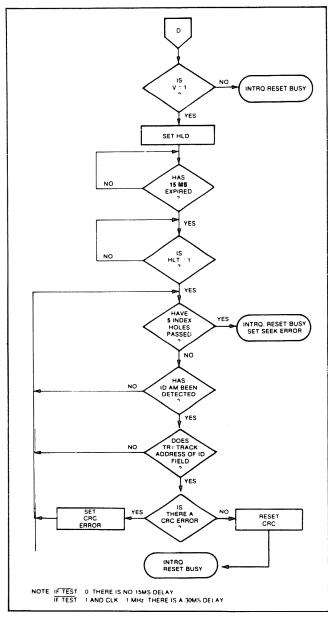

When a Seek, Step or Restore command is executed an optional verification of Read-Write head position can be performed by setting bit 2 (V = 1) in the command word to a logic 1. The verification operation begins at the end of the 15 millisecond settling time after the head is loaded against the media. The track number from the first encountered ID Field is compared against the contents of the Track Register. If the track numbers compare and the ID Field Cyclic Redundancy Check (CRC) is correct, the verify operation is complete and an INTRQ is generated with no errors. The FD179X must find an ID field with correct track number and correct CRC within 5 revolutions of the media; otherwise the seek error is set and an INTRQ is generated.

**Table 1. STEPPING RATES**

| CI | _K | 2 MHz  | 2 MHz  | 1 MHz  | 1 MHz  | 2 MHz  | 1 MHz  |

|----|----|--------|--------|--------|--------|--------|--------|

| DD | EN | 0      | 1      | 0      | 1      | x      | X      |

| R1 | R0 | TEST=1 | TEST=1 | TEST=1 | TEST=1 | TEST=0 | TEST=0 |

| 0  | 0  | 3 ms   | 3 ms   | 6 ms   | 6 ms   | 184µs  | 368µs  |

| 0  | 1  | 6 ms   | 6 ms   | 12 ms  | 12 ms  | 190μs  | 380µs  |

| 1  | 0  | 10 ms  | 10 ms  | 20 ms  | 20 ms  | 198µs  | 396µs  |

| 1  | 1  | 15 ms  | 15 ms  | 30 ms  | 30 ms  | 208μs  | 416µs  |

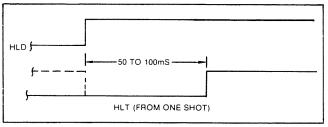

The Head Load (HLD) output controls the movement of the read/write head against the media. HLD is activated at the beginning of a Type I command if the h flag is set (h = 1), at the end of the Type I command if the verify flag (V = 1), or upon receipt of any Type II or III command. Once HLD is active it remains active until either a Type II command is received with (h = 0 and V = 0); or if the FD179X is in an idle state (non-busy) and 15 index pulses have occurred.

Head Load Timing (HLT) is an input to the FD179X which is used for the head engage time. When HLT = 1, the FD179X assumes the head is completely engaged. The head engage time is typically 30 to 100 ms depending on drive. The low to high transition on HLD is typically used to fire a one shot. The output of the one shot is then used for HLT and supplied as an input to the FD179X.

**HEAD LOAD TIMING**

When both HLD and HLT are true, the FD179X will then read from or write to the media. The "and" of HLD and HLT appears as a status bit in Type I status.

In summary for the Type I commands: if h=0 and V=0, HLD is reset. If h=1 and V=0, HLD is set at the beginning of the command and HLT is not sampled nor is there an internal 15 ms delay. If h=0 and V=1, HLD is set near the end of the command, an internal 15 ms occurs, and the FQ179X waits for HLT to be true. If h=1 and V=1, HLD is set at the beginning of the command. Near the end of the command, after all the steps have been issued, an internal 15 ms delay occurs and the FD179X then waits for HLT to occur.

For Type II and III commands with E flag off, HLD is made active and HLT is sampled until true. With E flag on, HLD is made active, an internal 15 ms delay occurs and then HLT is sampled until true.

### **DISK READ OPERATIONS**

Sector lengths of 128, 256, 512 or 1024 are obtainable in either FM or MFM formats. For FM, DDEN should be placed to logical "1." For MFM formats, DDEN should be placed to a logical "0." Sector lengths are determined at format time by a special byte in the "ID" field. If this Sector length byte in the ID field is zero, then the sector length is 128 bytes. If 01 then 256 bytes. If 02, then 512 bytes. If 03, then the sector length is 1024 bytes. The number of sectors per track as far as the FD179X is concerned can be from 1 to 255 sectors. The number of tracks as far as the FD179X is concerned is from 0 to 255 tracks. For IBM 3740 compatibility, sector lengths are 128 bytes with 26 sectors per track. For System 34 compatibility (MFM), sector lengths are 256 bytes/sector with 26 sectors/track; or lengths of 1024 bytes/sector with 8 sectors/track. (See Sector Length Table.)

For read operations, the FD179X requires RAW READ Data (Pin 27) signal which is a 250 ns pulse per flux transition and a Read clock (RCLK) signal to indicate flux transition spacings. The RCLK (Pin 26) signal is provided by some drives but if not it may be